FuturePlus Systems Corporation 2790 North Academy Blvd., Suite 307 Colorado Springs, CO 80917-5329 USA TEL:719-380-7321 FAX:719-380-7362 www.futureplus.com sales@futureplus.com tech\_sup@futureplus.com

#### **Current Activities**

Vice President of FuturePlus Systems Corporation. As an electrical engineer I am involved in both the hardware and software design of many of our products.

#### Author Background

BSEE and MSEE in Electrical Engineering. expertise My main area of is bus architectures. both I/O and multiprocessing. This has been the focus of my career for the past eleven years. FuturePlus Systems has been involved with PCI since 1993 and is a member of the PCI Special Interest Group. Our bus analysis products are used world-wide and all our products Hewlett-Packard carry part numbers. In addition to PCI, we havebus analysis products for: USB, ISA, AGP, RAMBUS, DIMM, SIMM, VME, VME64, IEEE 1394A and FIBRE CHANNEL.

Barbara P. Aichinger FuturePlus Systems 36 Olde English Road Bedford, NH 03110 TEL:603-472-9098 FAX:603-472-9097 e-mail:barb@futureplus.com

# Can I use a logic analyzer to debug my PCI system?

- Probes connect your PCI to the logic analyzer

- Software runs on the logic analyzer that transforms it into a bus analyzer

- A WEB connection allows for remote debugging and easy transfer of data to your application

Yes you can! With products from FuturePlus Systems and Hewlett-Packard Company.

# Compliance Violations

| - Li<br>Fil | s <mark>ting&lt;1&gt;</mark><br>.e Edit Opt |             | sm Source            |                 |            |             | □<br>>lp |

|-------------|---------------------------------------------|-------------|----------------------|-----------------|------------|-------------|----------|

|             |                                             | 0           | sm source            |                 |            | пе          | цþ       |

| Na          | vigate Gro                                  | up Run      |                      |                 |            |             |          |

| <u>_</u>    | earch Goto                                  | Markers     | Comments Analysis    | 1 Hours Com     | 1          |             |          |

| <u> </u>    |                                             |             |                      | s   Mixeu Signa | at i       |             |          |

| Go          | to Time 🛓                                   | ∐0 s        | 🛓 Goto               |                 |            |             |          |

|             | Trigger   Be                                | ginning     | End G1               | G2 (            |            |             |          |

| -           |                                             |             |                      |                 |            |             |          |

| _           |                                             |             |                      |                 |            |             |          |

|             | Time                                        | ADDR        | FUTUREPLUS SYSTEMS o | 1998            | ADDR_H     | AERROR IN   | N        |

|             | Relative                                    | Hex         | PCI BUS TRANSACTIONS | DEV 4 0         | Hex        | Binary Bi   | ;        |

|             | Relative                                    | Hex         | PUI BUS TRHNSHUTIONS | REV 1.2         | Hex        | Binary Bi   | 1        |

|             | 28.000 ns                                   | 730CF370    | IDLE                 |                 | 1FFFFF     | 1 1         | 1        |

|             | 32,000 ns                                   | 730CF370    |                      |                 | 1FFFFF     | 1 1         | 1        |

|             | 28,000 ns                                   | 730CF370    |                      |                 | 1FFFFF     | 1 1         | 1        |

|             | 32,000 ns                                   | 730CF374    | MEM READ ADR=730CF37 | 4               | 1FFFFF     | 1 1         | 1        |

|             | 28,000 ns                                   | 730CF374    | WAIT-NO DEVICE       | SELECT          | 1FFFFF     | 1 1         | 1        |

|             | 32,000 ns                                   | 730CF374    | WAIT-TARGET NOT      | READY           | 1FFFFF     | 1 1         | 1        |

|             | 28,000 ns                                   | 730CF374    | WAIT-TARGET NOT      | READY           | 1FFFFF     | 1 1         | 1        |

|             | 32,000 ns                                   | 730CF374    | WAIT-TARGET NOT      | READY           | 1FFFFF     | 1 1         | 1        |

|             | 28,000 ns                                   | 730CF374    | WAIT-TARGET NOT      |                 | 1FFFFF     | 1 1         | J.       |

|             | 32,000 ns                                   | 730CF374    | WAIT-TARGET NOT      | READY           | 1FFFF      | 1 1         | I        |

|             | 28,000 ns                                   | 730CF374    | WAIT-TARGET NOT      |                 | 1FFFFF     |             | 1        |

|             | 32,000 ns                                   | 730CF374    | WAIT-TARGET NOT      |                 | 1FFFFF     |             | 1        |

| r.          | 32,000 ns                                   | 730CF374    | WAIT-NO DEVICE       | SELECT          | 1FFEFF     |             | -1       |

|             | 28,000 ns                                   | 730CF374    | COMPLIANCE VIOLATION |                 | 1FFFFF     | 0 1         | 1        |

|             |                                             |             | RULE VIOLATION DETE  |                 |            |             | 1        |

|             | 28.000 ns                                   | 730CF374    | WAIT-TARGET NOT      | READY           | 1FFFFF     |             | 1        |

|             | 32,000 ns                                   | 730CF374    | D32=00000000         |                 | 1FFFFF     | 1 1         | 1        |

|             | 1                                           | 1           |                      | (               |            | 1           | 1        |

| Sta         | rt Session Mana                             | ager 16700A | Logic Workspace      | Timing Zoom<1>  | Listing<1> | Waveform<1> |          |

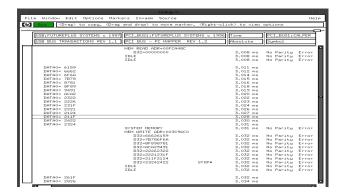

Compliance violation triggering is available on many PCI test tools today. The key to making this feature useful is to be able to quickly determine the cause of a violation.

Compliance Violation Triggering

If a tool tells you a violation has occurred, that is good, but being able to trigger on a violation and see it is better. A mask to filter out known violations can also help to characterize the design you are debugging. What if a violation does occur? How do you dig deeper to find the root cause of the problem? In the trace on the previous slide we saw an illegal deassertion of DEVSEL#. Is this a chip problem? A board problem? A timing problem? A software problem? A backplane issue? A routing problem? How many times have engineers said. "If I could find it ... I could fix it...but the problem is I can't find it!" OR " I spend 90% time looking for the problem and only 10% of my time fixing it."

With a logic analysis system you can quickly track the problem down and solve it.

Signal Integrity

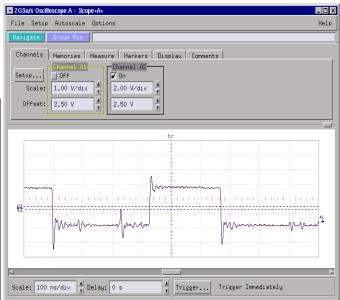

Cross-domain analysis is being able to go from the the state per clock or state per transaction domain to the timing domain and to the analog domain. Here we can actually see the glitch on DEVSEL#. Not what you expected I bet.

Chapter 4 of the PCI Specification covers the electrical environment for PCI. Signal Integrity investigation is most important in high volume applications where variation in parts, connectors, capacitors and resistors can cause failures. These types of failures sometimes show up in manufacturing but in some cases show up in the field when the user tries to install his new PCI board in his existing PCI based system. As all high volume consumer manufacturers know, failures in the field are the most expensive to fix. Costs for customer service, support and field replacement of boards can be astronomical. In addition, a company's reputation for quality can be severely tarnished.

For PCI, a robust signal integrity analysis of the design is a cost effective step in the overall design and verification process.

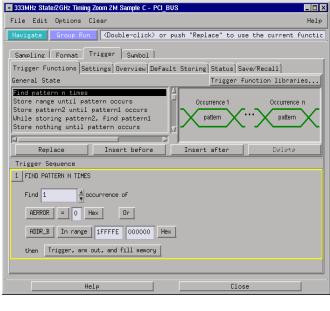

## Timing Analysis

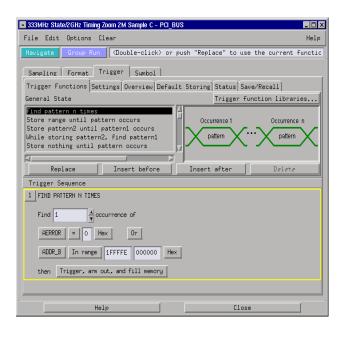

File Edit Options Clean Help <Double-click> or push "Replace" to use the current functic Sampling Format Trigger Symbol Trigger Functions Settings Overview Status Save/Recall Trigger function libraries.. General Timing Find pattern Occurrence 1 Find edge Find edge AND pattern Find width violation on pattern/pulse Find Nth occurrence of an edge event Replace Insert before Insert after Delete Trigger Sequence 1 FIND GLITCH Find DEVSEL Edge 1 Or FRAME Edge † Or IRDY Edge † Or TRDY Edge 🕇 Or STOP Edge 1 Help Close

Setup and hold violation triggering can also be done by a logic analysis system. However, let's take that one step further with glitch detection. Glitches from misaligned state machines, bus contention, timing problems or signal integrity issues can be missed if your only looking for setup and hold violations. What if the problem does not occur near a rising clock edge? Does that mean it is not a problem? Glitches can propagate through logic and cause errors.

The new HP 16715A, 16716A, and 16717A modules from HP allow for glitch detection on any signal and then a 2Gs/s Timing Zoom to see the problem up close.

| Glitch on DEVSEL |                                            | _ 🗆 × |

|------------------|--------------------------------------------|-------|

| File Edit Opt    | ions                                       | Help  |

| Navigate         | Run                                        |       |

| Search   Goto    | Markers Comments Analysis Mixed Signal     |       |

| G1: ADDR         | ↓ = 73FF Time ↓ from Trigger ↓ = -1.568 ns | A     |

| G2: ADDR         | ₹ = 8C00 Time t from Trigger t = 1,470 ns  | V     |

| Seconds/div =    | 5,000 ns A Delay 0 s A                     |       |

|                  | G1trG2                                     | Л     |

| PCICLK all       | 1 0 1 0                                    | Ĩ     |

| DEVSEL all       | 0 0                                        |       |

| DEVSEL_TZ all    | 0 1 0                                      | -     |

| IDSEL all        | 1 0                                        |       |

| IDSEL_TZ all     | 1 0                                        |       |

| STOP all         | 1                                          |       |

| FRAME all        |                                            |       |

| DATA_TZ all      | 73FF 0000                                  |       |

|                  |                                            |       |

| F                |                                            |       |

#### **Glitch Detection**

Here is that glitch on DEVSEL#. As you can see it is after the rising edge of the PCI clock. Technically not a hold violation (the spec says 0ns hold). However if the system had a 2ns clock skew, allowable by the spec, this could be a problem elsewhere on the board, inside a chip or elsewhere in the system.

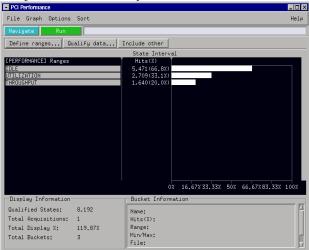

# Performance Analysis

Most all PCI tools today can give you Bus Utilization, Throughput and Efficiency as you can see here. But what if you don't like what you see? Can you dig deeper to see where the problem lies? Can you find the area of your design or system where improvements can be made?

# Bus Utilization : a more detailed picture

| PCI CYCLE TYPE              |             |                                         |         |        | _ 🗆 🗡   |

|-----------------------------|-------------|-----------------------------------------|---------|--------|---------|

| File Graph Options          | Sort        |                                         |         |        | Help    |

| Navigate Run                |             |                                         |         |        |         |

| Define ranges Qu            | alify data  | include othe                            | r       |        |         |

|                             | State I     | nterval                                 |         |        |         |

| [BUS_UT] Ranges             | Hits(%)     | Ϋ́.                                     |         |        |         |

| DATA_VALID                  | 1,992(43,4) | 0                                       |         |        |         |

| WAIT_NODVSL                 | 993(21.6)   | 0                                       |         |        |         |

| ADD_CYC                     | 993(21,6)   |                                         |         |        |         |

| WAIT_INITIATOR              | 614(13.4)   |                                         |         |        |         |

| IDLE                        | 0(0.0)      |                                         |         |        |         |

| WAIT_TARGET<br>MASTER_ABORT | 0(0.02      |                                         |         |        |         |

| RETRY                       | 0(0.02      |                                         |         |        |         |

| TARGET ABORT                | 0(0.0)      |                                         |         |        |         |

| THIKGET_INDOKT              |             | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |         |        |         |

|                             |             |                                         |         |        |         |

|                             |             |                                         |         |        |         |

|                             |             | 0% 20%                                  | 40%     | 60% 80 | 0% 100% |

|                             |             | Bucket In                               | formati | .on    |         |

| Qualified States:           | 4,592       | Name:                                   |         |        |         |

| Total Acquisitions:         | 1           | Hits(%):                                |         |        |         |

|                             |             | Range:                                  |         |        |         |

| Total Display %:            |             | Min/Max:                                |         |        |         |

| Total Buckets:              | 9           | File:                                   |         |        |         |

|                             |             | Lite:                                   |         |        | M       |

With a logic analysis system you can! A cycle by cycle breakdown of Bus Utilization can quickly help you characterize your design or that new add-in card you just added to the system. You can take this view one step further and dig even deeper. You can qualify this type of a display to show only the Bus Utilization of a certain bus master or by accesses to certain address ranges or even further qualify it by transaction type (Memory Writes for example).

| PCI Transactions    |            |                         | ×  |

|---------------------|------------|-------------------------|----|

| File Graph Options  | Sort       | Hel                     | p  |

| Navigate Run        |            |                         |    |

| Define ranges Qu    | alify data | Include other           |    |

|                     | State      | te Interval             |    |

| [L_CMD] Ranges      | Hits(%)    | )                       | A. |

| MEM_WR              | 65,534(50  | 0,0%)                   |    |

| I/O_RD              | 64,683(49  | 9,3%)                   |    |

| I/O_WR              | 806(0      |                         |    |

| INTACK              |            | 0.02)                   |    |

| CON_RD              |            | 0.0%)                   |    |

| CON_WR              |            | 0.0%)                   |    |

| DAD_CY<br>MEMRDL    |            | 0.02)                   |    |

| MEMRDM              |            | 0.02)                   |    |

| MEMWRI              |            | 0.0%)                   |    |

| MEM_RD              |            | 0.0%)                   |    |

| RESRVD              |            | 0.0%)                   | v  |

|                     |            | 07 207 407 607 807 1007 |    |

|                     |            | Bucket Information      |    |

| Qualified States:   | 131.072    | Name:                   | Δ  |

| Total Acquisitions: | 1          | Hits(%):                |    |

|                     | -          |                         |    |

| Total Display %:    | 100,00%    | Range:<br>Min/Max:      |    |

| Total Buckets:      | 16         |                         |    |

|                     |            | File:                   | 1  |

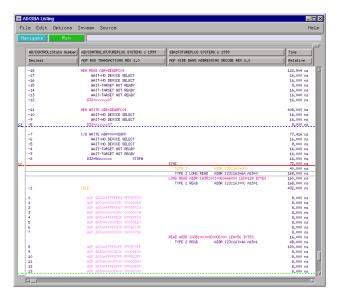

#### *Throughput: a more detailed picture*

Throughput is a measurement of what percentage of the time data is actually being transferred over the bus. But how is it being transferred? What transactions are being used? What bus master is responsible for which percentage of the throughput?

These questions can all be answered by using your logic analysis system.

PCI has has come along way since 1993. At the first Compliance Workshop folks were just happy that the data got transferred correctly. Now entire systems depend on the reliability and performance of the PCI bus. Most PCI based systems today have several PCI buses or PCI buses connected to other I/O and memory buses. How do you validate the entire system? Your logic analysis system has the capability to do just that.

First let's discuss Cross Domain Analysis. That is what we saw earlier. This helps determine if we have a simple logic bug, a timing problem or an analog signal integrity problem. Cross Bus analysis is what we will look at next. This helps us track the data as it goes from bus to bus through the system.

The last area we will touch on is tracking the source code that is running on the system right down to the PCI bus.

PCI to USB

Here is how we can track data from the PCI bus out onto the USB.

This state listing shows USB isochronous traffic from a USB Camera through the host chip set and onto the PCI. Note that the PCI bridge asserts stop after 32 bytes and the USB has 64 bytes to transfer.

#### AGP4X

For those of you involved in graphics design you will recognize this technology. The AGP specification was based on PCI and PCI traffic can be seen here. The AGP4X data is shown in purple and the Side Band Addressing bus is cross-bus correlated in real-time to the AGP bus so that accurate addressing information can be seen.

## State Analysis at 66Mhz

|    | <mark>CIBus Sampl</mark><br>Le Edit I | e Trace<br>Dptions Invasm Source |          | <br>He      |     |

|----|---------------------------------------|----------------------------------|----------|-------------|-----|

| _  |                                       |                                  |          | ne          | - 1 |

| Na | vigate                                | Run                              |          |             |     |

|    | ADDR                                  | FUTUREPLUS SYSTEMS c 1998        | AERROR   | Time        | Г   |

|    | Hex                                   | PCI BUS TRANSACTIONS REV 1.      | 2 Binary | Relative    |     |

|    |                                       | <b>/</b>                         | <u> </u> | <u> </u>    | 1   |

|    | 00680210                              | MEMRD LINE ADR=006BD21C          | 1        | 2.752 us    | -II |

|    | 006BD21C                              | D32=xxxFExx                      | 1        | 624.000 ns  | J.  |

|    | OODDEIC                               | 535-00001 E00                    | *        | 024.000 113 | R   |

|    | 006BFAC0                              | MEMRD MUL ADR=006BFAC0           | 1        | 5.240 us    | J.  |

|    | 006BFAC0                              |                                  | 1        | 512.000 ns  | J.  |

|    | 006BFAC4                              | D32=00000000                     | 1        | 24.000 ns   | J.  |

| -  | 006BFAC8                              |                                  | 1        | 32.000 ns   | 11  |

|    | 006BFACC                              | D32=00000000                     | 1        | 32,000 ns   | J.  |

|    | 006BFAD0                              | D32=00000001                     | 1        | 32,000 ns   | н   |

|    | 006BFAD4                              | D32=006B5000                     | 1        | 24.000 ns   | 1   |

|    | 006BFAD8                              | D32=00000200                     | 1        | 32.000 ns   | J.  |

|    | 006BFADC                              | D32=00008801                     | 1        | 32.000 ns   | I   |

|    | 006BFAC0                              | MEM WRITE ADR=006BFAC0           | 1        | 42.112 us   | J.  |

|    | 006BFAC0                              | D32=8A000064                     | 1        | 56.000 ns   | н   |

|    | 006BFAC4                              | D32=00000000                     | 1        | 32,000 ns   | 1   |

|    | 006BFAC8                              | D32=00000028                     | 1        | 32,000 ns   | 1   |

|    | 006BFACC                              | D32=0000000                      | 1        | 32.000 ns   | н   |

|    | 006BFAD0                              | D32=00000001                     | 1        | 24,000 ns   | J.  |

|    | 006BFAD4                              | D32=006B5000                     | 1        | 32,000 ns   | н   |

|    | 006BFAD8                              | D32=00000200                     | 1        | 32,000 ns   | н   |

|    | 006BFADC                              | D32=××008801                     | 1        | 32,000 ns   | I   |

|    | 02FF0000                              | SPECIAL CYCLE                    | 1        | 256.632 us  | 1   |

|    | 02FF0000                              | HALT                             | 1        | 24.000 ns   | JI. |

|    |                                       | MESSAGE DATA=02FF                |          |             | Jł. |

|    | 02FF0000                              | HALT                             | 1        | 32.000 ns   | 1   |

|    |                                       | MESSAGE DATA=02FF                |          |             | 1   |

|    | 02FF0000                              | HALT                             | 1        | 32.000 ns   | JI. |

|    |                                       | MESSAGE DATA=02FF                |          |             | 1   |

|    | 02FF0000                              | HALT                             | 1        | 24.000 ns   | j,  |

High end PCI system analysis can greatly benefit from a logic analysis system. PCI at 66Mhz can be accurately characterized and debugged with the new HP 16715A, 16716A, and 16717A modules from HP with the 2GHz Timing Zoom.

What happens if you want to trigger on a specific address but sometimes that address falls within a burst? Because of system retries and position independent code you don't know where in the burst that address occurs. You can try to add code to print out key data patterns and trigger on those as I used to do (my favorite data pattern was FEEDFACE) or you can use some of the newer PCI debug tools that increment the address during a burst to the logic analyzer.

# RAMBUS

|             | ions Invasm Source            | н |

|-------------|-------------------------------|---|

| vigate      | Run                           |   |

| State Numbe | r RAMBUS TRANSACTIONS REV 0.8 |   |

| Decimal     | ROW COLUMN DATA               |   |

| -1323       | ROWA DR=00 BR=04 R10:0=0BE    |   |

| -1322       | COLC WR DC=00 BC=08 AC=2A     |   |

|             | COLM MA=10 MB=00              |   |

| -1321       |                               |   |

| -1320       | D31:00=4D550000               |   |

|             | D63:32=54530043               |   |

|             | D95:64=5444492D               |   |

| -1319       | D127:96=6E655000              |   |

| -1319       | COLC NOCOP DC=00 BC=08 AC=2A  |   |

| -1310       | COLM MA=00 MB=10              |   |

| -1317       | COEN NHEOO NDEIO              |   |

| -1316       | D31:00=296E506F               |   |

|             | B63:32=00420000               |   |

|             | D95:64=54444900               |   |

|             | D127:96=6E655000              |   |

| -1315       |                               |   |

| -1314       | COLC NOCOP DC=00 BC=08 AC=2A  |   |

|             | COLM MA=20 MB=00              |   |

| -1313       | D31:00=2965506F               |   |

| -1312       | D63:32=00420000               |   |

|             | D5152-00420000                |   |

|             | D127:96=6E655000              |   |

| -1311       | D127,100-02000000             |   |

| -1310       | COLC RD DC=00 BC=04 AC=07     |   |

|             | COLX NOXOP DX=00 BX=00        |   |

| -1309       |                               |   |

| -1307       |                               |   |

| -1296       | D31:00=6D756D75               |   |

|             | D63:32=00490049               |   |

|             | D95:64=746E746E               |   |

|             | D127:96=2D6D2D6D              |   |

| -1295       |                               |   |

Tracking data to and from memory? Only a properly designed logic analysis system can handle the 400Mhz RAMBUS technology.

# *IEEE 1394A*

| il | e Edit Options Invasm Source           |         |      |        |       | He.   |

|----|----------------------------------------|---------|------|--------|-------|-------|

| Na | vigate Run                             |         |      |        |       |       |

|    | FUTUREPLUS SYSTEMS c 1998              | Time    | Time |        | TCODE | SPEED |

|    | IEEE 1394 BUS TRANSACTIONS VERSION 1.1 | Relativ | e    | Binary | Hex   | Hex   |

|    | ARB Reset Gap                          |         |      |        |       |       |

|    |                                        | 102,624 | us   | 1      | 18    | 1     |

|    | CYCLE_START @S100:                     |         |      |        |       |       |

|    | TLABEL= 00H; RETRY CODE= retry_1       |         |      |        |       |       |

|    | DST ID:Bus= 3FFH:Node= 3FH             |         |      |        |       |       |

|    | SRC_ID:Bus= 3FFH;Node= 02H             | 40,000  | ns   | 1      | 18    | 1     |

|    | DST_OFFSET= CYCLE_TIME register        | 280,000 | ns   | 1      | 18    | 1     |

| 1. | Cucle Time Data= F687F029H             | 352,000 | ns   | 1      | 18    | 1     |

|    | HDR CRC ERR:RCVD CRC= 5E03B361H        | 360,000 |      | 1      | 18    | 1     |

|    |                                        | 10.824  | us   | 0      | 02    | 1     |

|    | SUBACTION Gap                          |         |      |        |       |       |

|    |                                        | 10,504  | us   | 0      | 01    | 1     |

|    | ARB Reset Gap                          |         |      |        |       |       |

| r  |                                        | 72,368  | us   | 1      | 14    | 1     |

|    | RD_REQ_DATA_QUADLET @S100:             |         |      |        |       |       |

|    | TLABEL= 03H; RETRY CODE= retry_1       |         |      |        |       |       |

|    | DST_ID:Bus= 3FFH:Node= 01H             |         |      |        |       |       |

|    | SRC_ID:Bus= 3FFH;Node= 02H             | 40,000  | ns   | 1      | 14    | 1     |

| 2  | DST_OFFSET= FFFFF0000400H              | 280,000 | ns   | 1      | 14    | 1     |

|    | HDR CRC ERR:RCVD CRC= 39FFA4AAH        | 392,000 | ns   | 1      | 14    | 1     |

|    |                                        | 608,000 | ns   | 0      | 0C    | 1     |

|    | ACK Packet: ack_pending                |         |      |        |       |       |

|    |                                        | 10.848  | us   | 0      | 02    | 1     |

|    | SUBACTION Gap                          |         |      |        |       |       |

|    |                                        | 3,744   | us   | 1      | 16    | 1     |

|    | RD_RESPONSE_QUADLET @S100;             |         |      |        |       |       |

|    | TLABEL= OCH; RETRY CODE= retry_1       |         |      |        |       |       |

|    | DST_ID:Bus= 3FFH:Node= 02H             |         |      |        |       |       |

|    | SRC_ID:Bus= 3FFH:Node= 01H             | 40,000  | ns   | 1      | 16    | 1     |

|    | RESP CODE: Response Complete           |         |      |        |       |       |

|    | Reserved Quadlet: 00000000H            | 280,000 | ns   | 1      | 16    | 1     |

|    | DATA= 01005030H                        | 352,000 | ns   | 1      | 16    | 1     |

|    | HDR CRC: E8B8626EH                     | 360,000 | ns   | 1      | 16    | 1     |

Using PCI to connect to IEEE 1394A? No problem! A logic analysis system can handle the job.

Can a software engineer benefit from a logic analysis system? The "hardware only" glass ceiling has been broken! Manufacturers of logic analysis systems are greatly motivated to serve the needs of the software engineer...and why? Software engineers now outnumber hardware engineers.

# Full featured triggering

Triggering now includes 16 level sequencer 4-way branching 2 global counters 2 global timers 1 level counter 16 patterns If-Then -Else Branching Triggers store and recall Pre-stored trigger macros

# PCI Post Processing

| 🖃 Invasm Preferences - PCI Bus Sample Trace   |

|-----------------------------------------------|

| PCI Bus Analysis Preferences                  |

| FS2102_3:File In<1>:Frame 10:Slot A:PCI_BUS   |

| Preference settings                           |

| PC MAPPER ADDRESS DECODE SUPPRESS PC MAPPER - |

| COMPLIANCE VIOLATIONS SHOW pods 9/10 req'd =  |

|                                               |

|                                               |

|                                               |

| Apply Reset Close                             |

| 🗕 Invasm Filter - PCI Bus Sample Trace 🛛 🔀                                     |

|--------------------------------------------------------------------------------|

| PCI Bus Analysis Filter Options<br>FS2102_3:File In<1>:Frame 10:Slot A:PCI_BUS |

| FS2102_3;F11e In(1);Frame 10;S1ot H;FC1_B05                                    |

| Show states of type                                                            |

| WAIT CYCLES Color                                                              |

| F IDLE CYCLES Color                                                            |

| I/O READS Color                                                                |

| I/O WRITES Color                                                               |

| MEMORY READS Color                                                             |

| MEMORY WRITES Color                                                            |

| CONFIGURATION READS Color                                                      |

| CONFIGURATION WRITES                                                           |

| F ALL OTHERS Color                                                             |

| COMPLIANCE VIOLATIONS Color                                                    |

|                                                                                |

| Apply Reset Close                                                              |

With the deep memory options available on PCI tools, post processing filters make it easy to remove all but the transactions of interest. Also the address mapping of common I/O and memory addresses help navigate through megabytes of acquired PCI traffic.

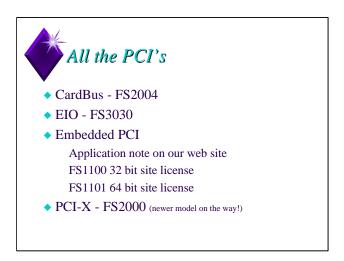

Which PCI are you doing? FuturePlus and Hewlett-Packard have teamed up to offer the broadest PCI tool offering in the industry.

For more information about the tools mentioned in this presentation please contact: your nearest Hewlett-Packard sales office or

FuturePlus Systems Corporation 2790 North Academy Blvd., Suite 307 Colorado Springs, CO 80917-5088 TEL:719-380-7321 FAX:719-380-7362 www.futureplus.com e-mail: sales@futureplus.com

Embedded PCI? No problem we can show you how.

Do you think PCI-X is in your future? Give us a call...it's in our future too!